# PHYSIQUE DES COMPOSANTS SEMI-CONDUCTEURS

X) FET et MOSFET: partie 1

P.A. Besse

**EPFL**

# Historique du MOSFET

• **1926** – Concept du FET

J. Lilienfeld (US patent)

• • •

. . .

1960 – Premier MOS

D. Kahng (US patent)

1963 - Invention du CMOS

F.M. Wanlass et C.T. Sah

• 1964 – Premier MOS IC commercial

General Microelectronics

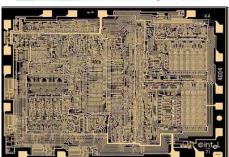

• 1971 – Premier microprocesseur

Intel i4004: 2300 transistors

2007 – Intel Itanium 2

> 1 milliard de transistors

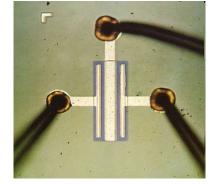

Fairchild FI 100 PMOS transistor

First commercial

with 120 PMOS

MOS IC,

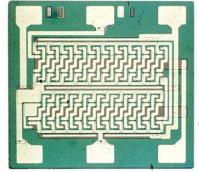

# VLSI (Very Large Scale Intgegration)

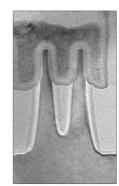

#### FinFET by Intel

<u>90 nm</u> 2003

65 nm

13 metal layers

http://download.intel.com/newsroom/kits/14nm/ pdfs/Intel 14nm New uArch.pdf

http://www.chipworks.com/en/technical-competitive-analysis/ resources/blog/intels-14-nm-parts-are-finally-here/

M. Bohr «Intel's Revolutionary 22 nm Transistor Technology», INTEL May 2011

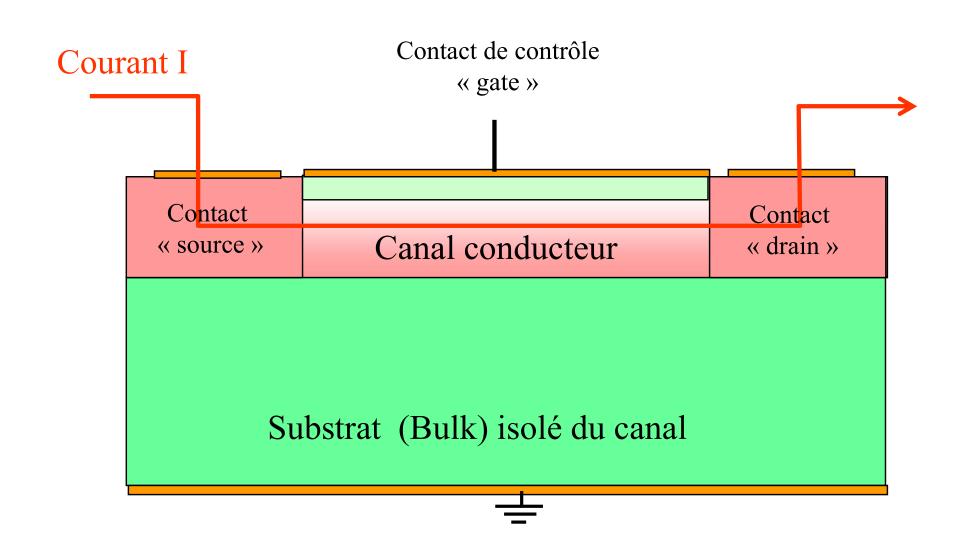

# 10.1: Principe du Field Effect Transistor (FET)

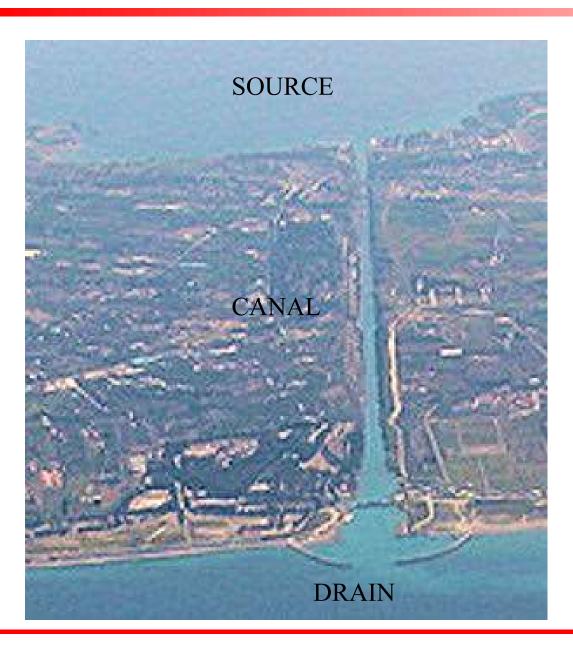

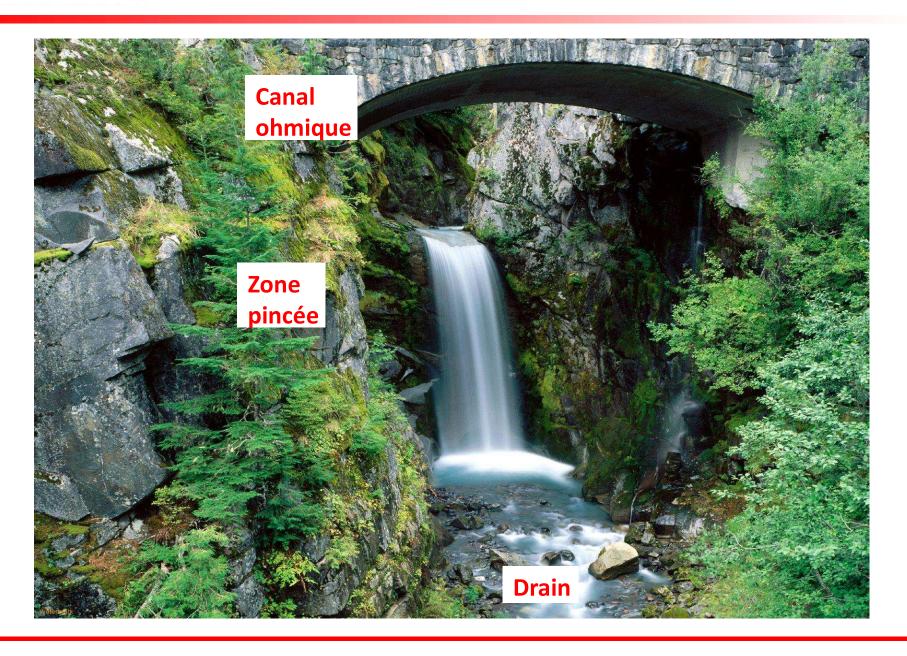

# Analogie: FET

Canal de Corinthe

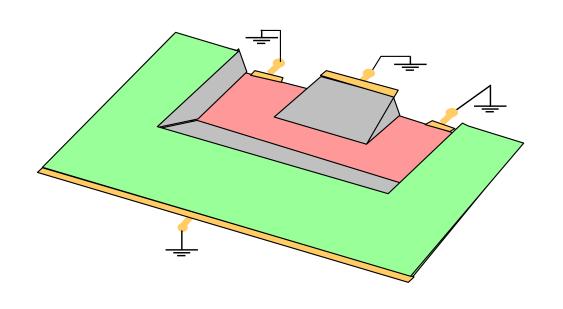

# Exemple 1: le NMOS

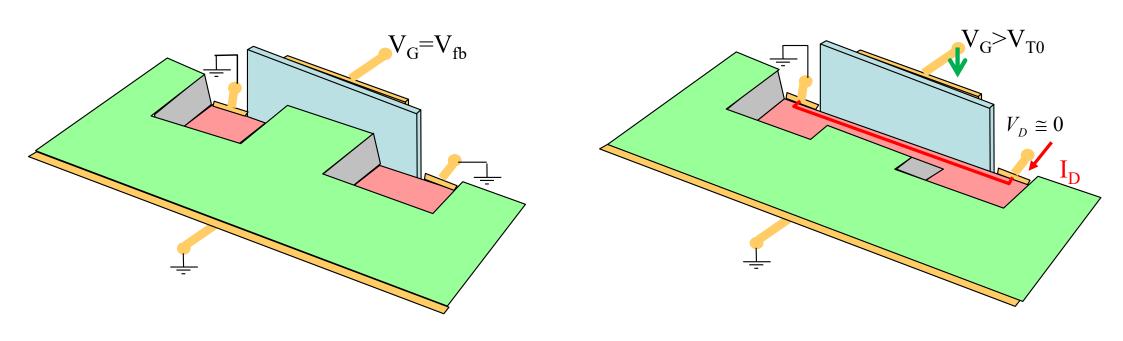

#### Attirer des électrons dans le canal

## Le NMOS, un "enhancement" FET

#### Bande de conduction

Sans tension de gate

Le canal n'existe pas

Avec tension de gate

Le canal est créé

# Exemple 2: le JFET à canal n

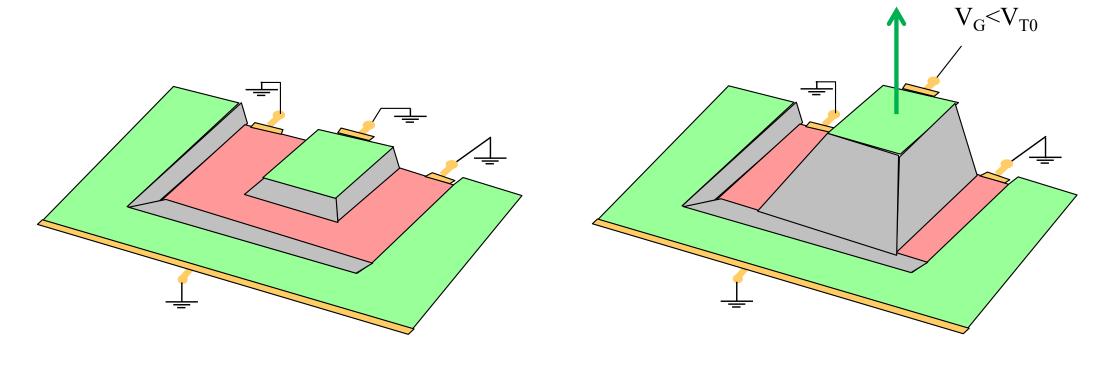

# Le JFET à canal n: un « depletion » FET

Bande de conduction

Sans tension de gate

Le canal existe

Avec tension de gate

Le canal disparait

## MESFET à canal n

## MESFET à canal n

Bande de conduction

Sans tension de gate

Le canal existe

Avec tension de gate

Le canal disparait

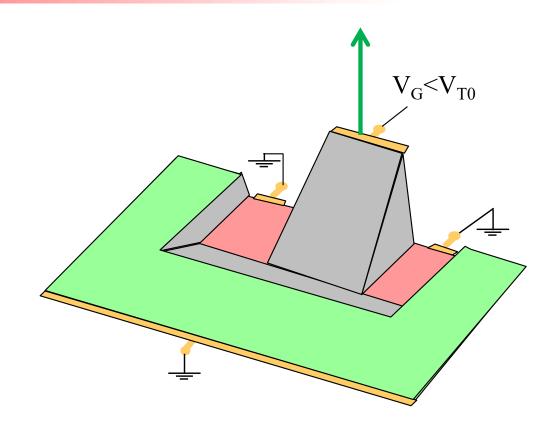

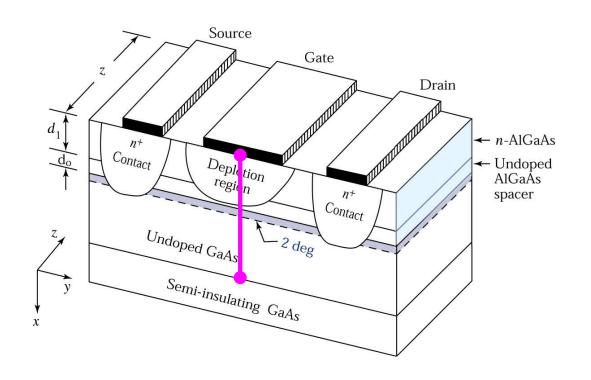

# High Electron Mobility Transistors (HEMT)

Semiconductor Devices, 2/E by S. M. Sze

Semiconductor Devices, 2/E by S. M. Sze

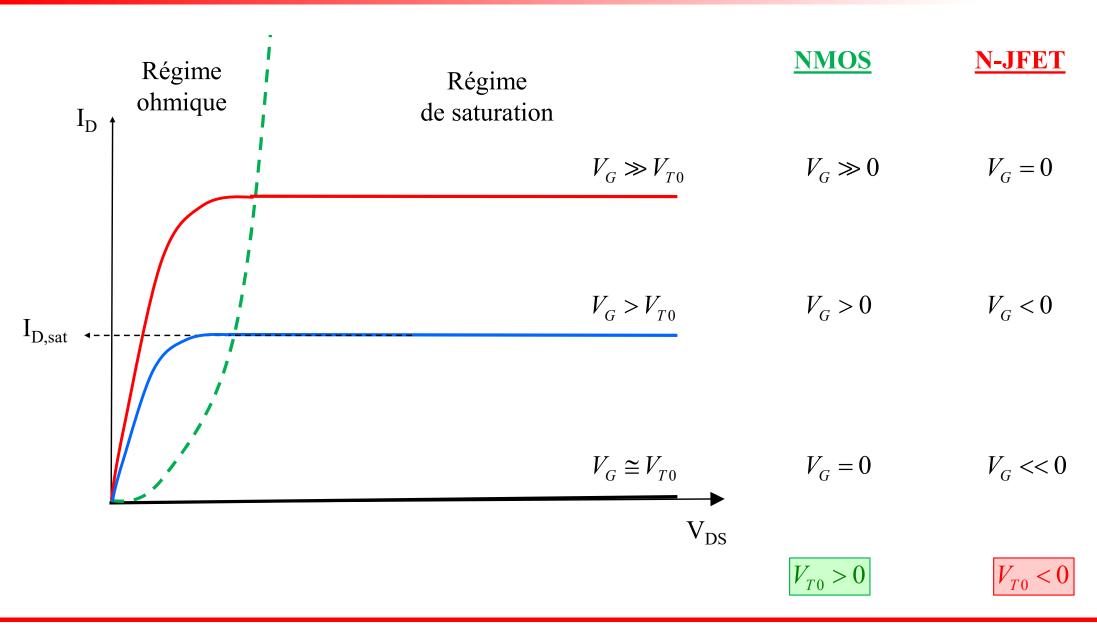

# Courbes de sortie des FET idéaux (canal n)

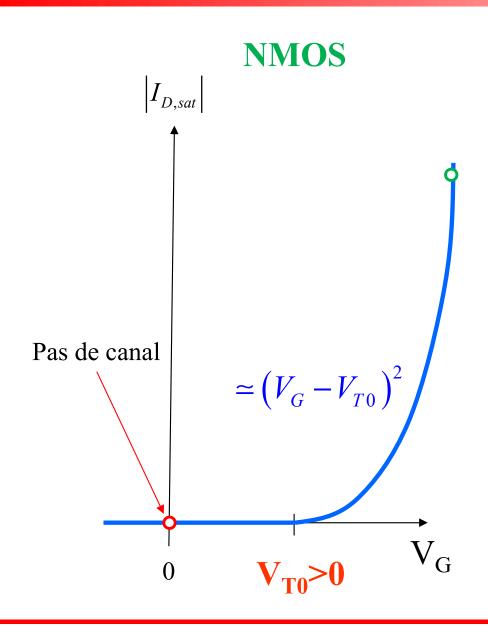

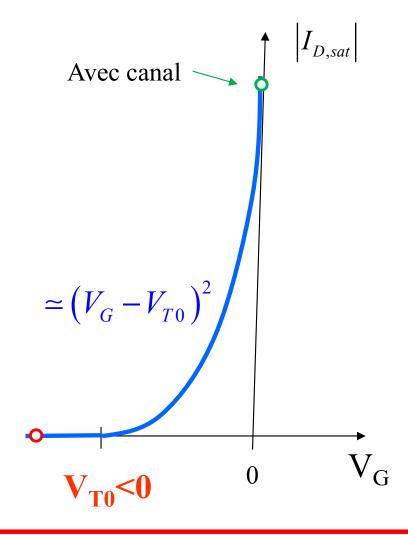

# Tension de threshold et courbe $I_{D,sat}(V_G)$

#### JFET à canal N

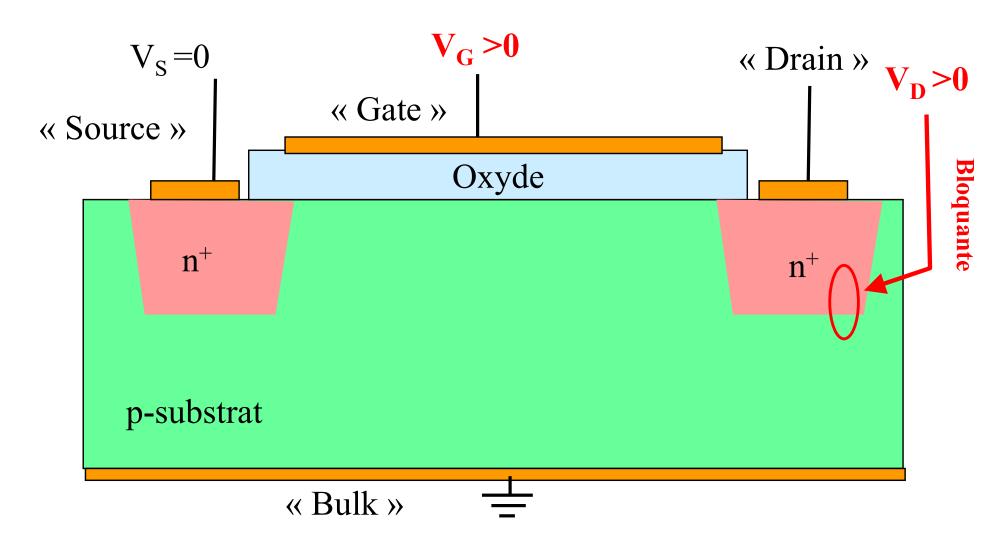

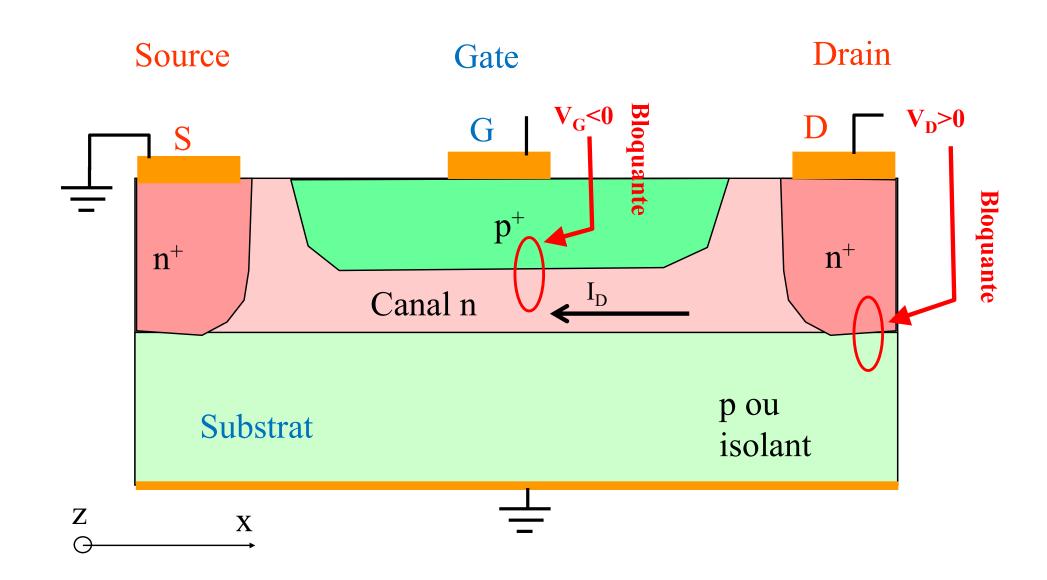

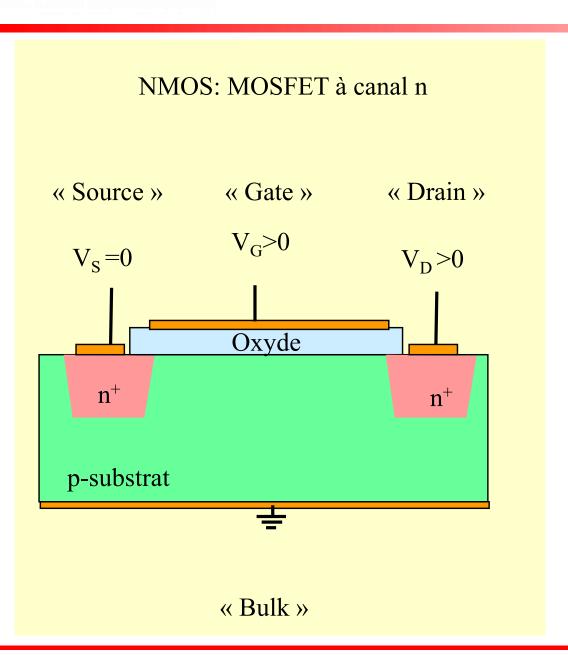

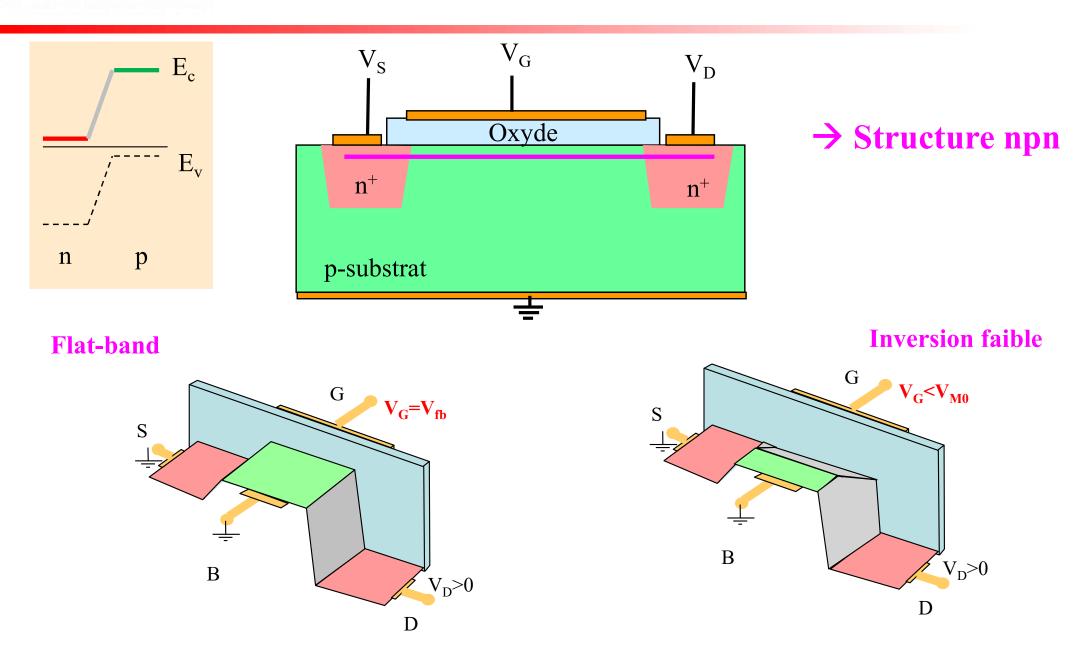

#### 10.2: Structure MOSFET

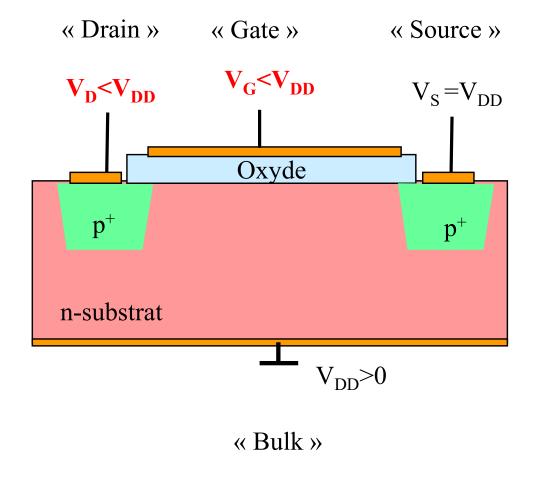

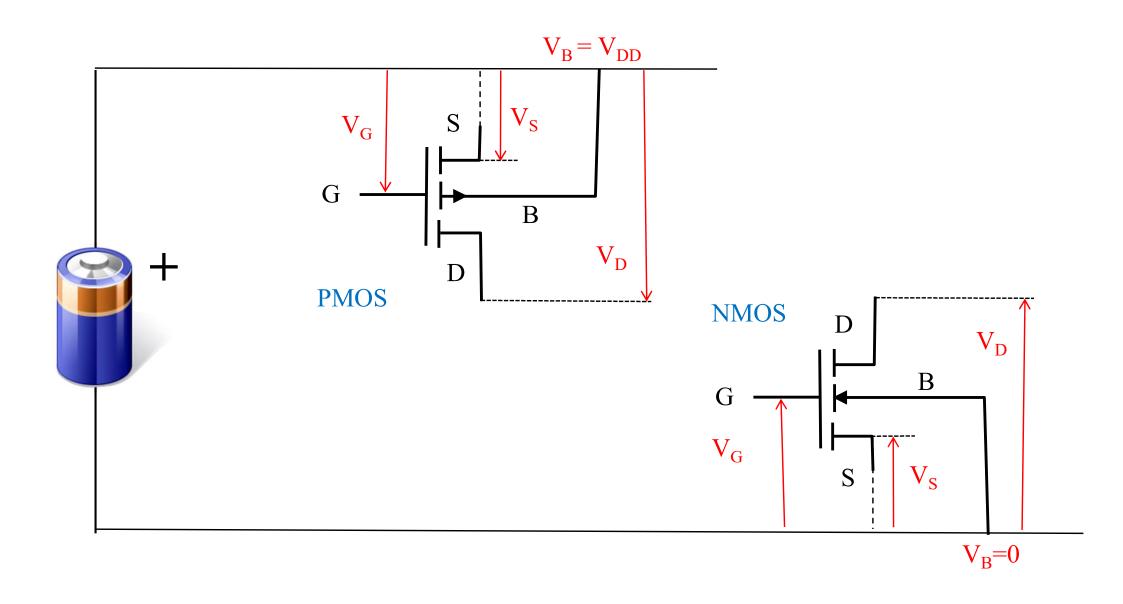

PMOS: MOSFET à canal p

## MOSFET: définition des tensions

# NMOS

*2/E* by S. M. Sze

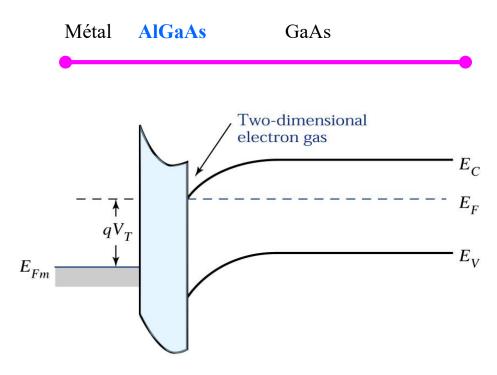

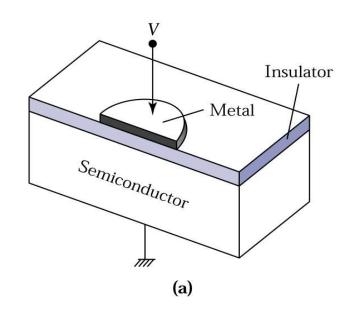

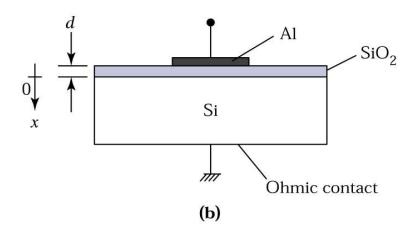

## Rappel: structure MOS

S. Sze « Semiconductor devices »

"Metal"

Al, Au, (electromigration)

Poly-Si, Silicide

**Oxide**

SiO<sub>2</sub>, High k (HfSiON)

$$d_{ox} \cong 10 \, nm$$

$$C_{ox} = \mathcal{E}_r \mathcal{E}_0 \frac{A}{d_{ox}}$$

$$\mathcal{E}_r \cong 4 \quad (SiO_2)$$

Semiconductor

Silicon

$$N \approx 10^{16} \ cm^{-3} \rightarrow 10^{18} \ cm^{-3}$$

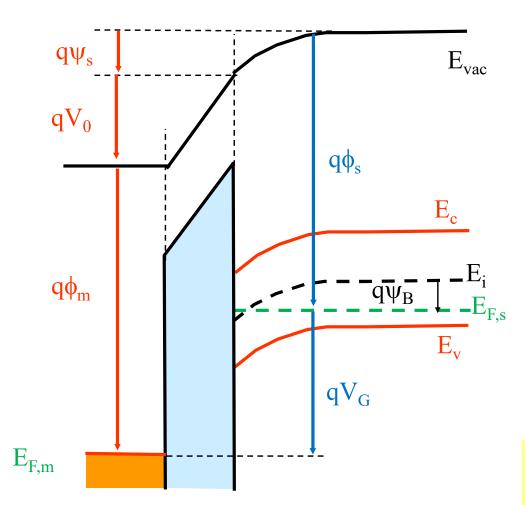

## Rappel: Potentiels et tensions

#### Potentiel sur le métal V<sub>G</sub>:

$$\frac{V_G + \phi_s = \psi_s + V_0 + \phi_m}{\vdots}$$

$$V_{M0} - V_{fb} = 2\psi_B \cdot (2n - 1)$$

$$\vdots$$

$$V_G - V_{M0} \cong n \cdot (\psi_s - 2\psi_B) - \frac{Q_n}{C_{ox}}$$

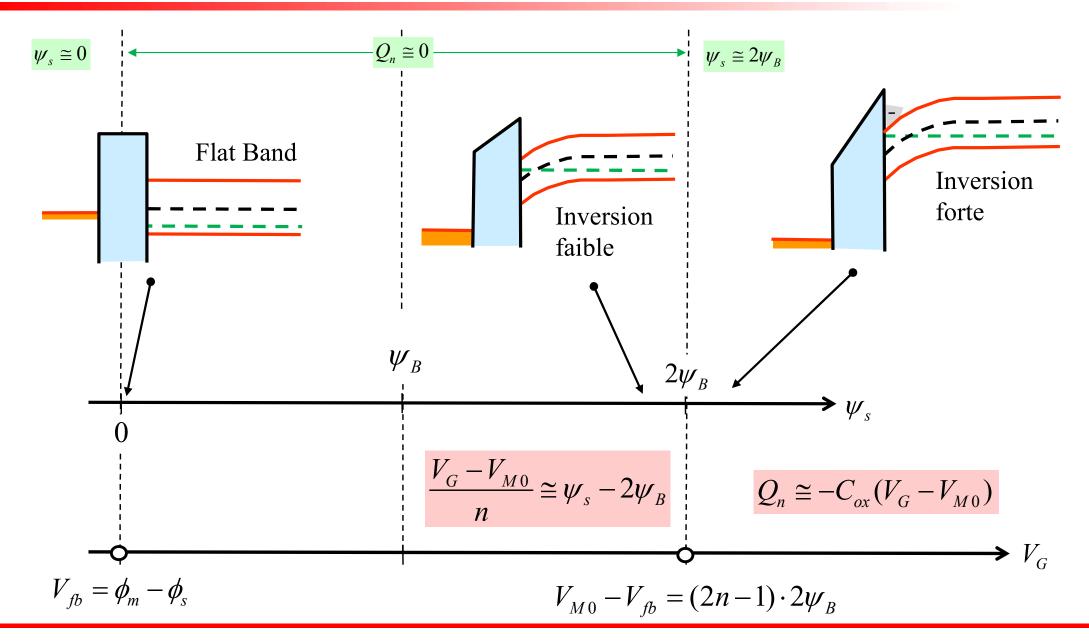

# Rappel: Inconnues et équations pour une jonction MOS sur substrat p

### 2 inconnues

A) Potentiel de surface  $\psi_s$ :

$\psi_{s}$

B) Charge libre à l'interface Q<sub>n</sub> reliée au potentiel sur l'oxyde

$Q_n$

#### Threshold

P.A. Besse, EPFL

$$V_{M0} - V_{fb} = 2\psi_B \cdot (2n-1)$$

## 2 équations en fct de V<sub>G</sub>:

1)

$$V_G - V_{M0} \cong n \cdot (\psi_s - 2\psi_B) - \frac{Q_n}{C_{ox}}$$

2) Approximations

- Accumulation

$$\psi_s \cong 0$$

- Déplétion

- Inversion faible

$$Q_n = 0$$

- Déplétion profonde

- Inversion forte

$$\psi_s \cong 2\psi_B$$

# Résumé: Formules avec slope factor n

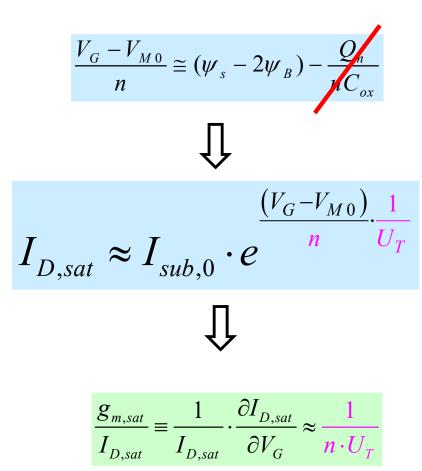

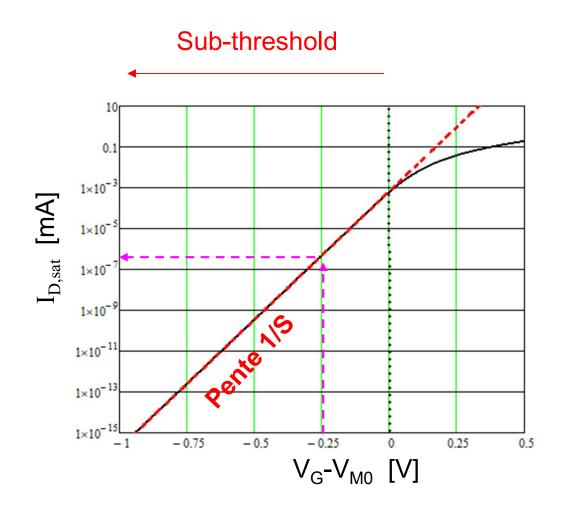

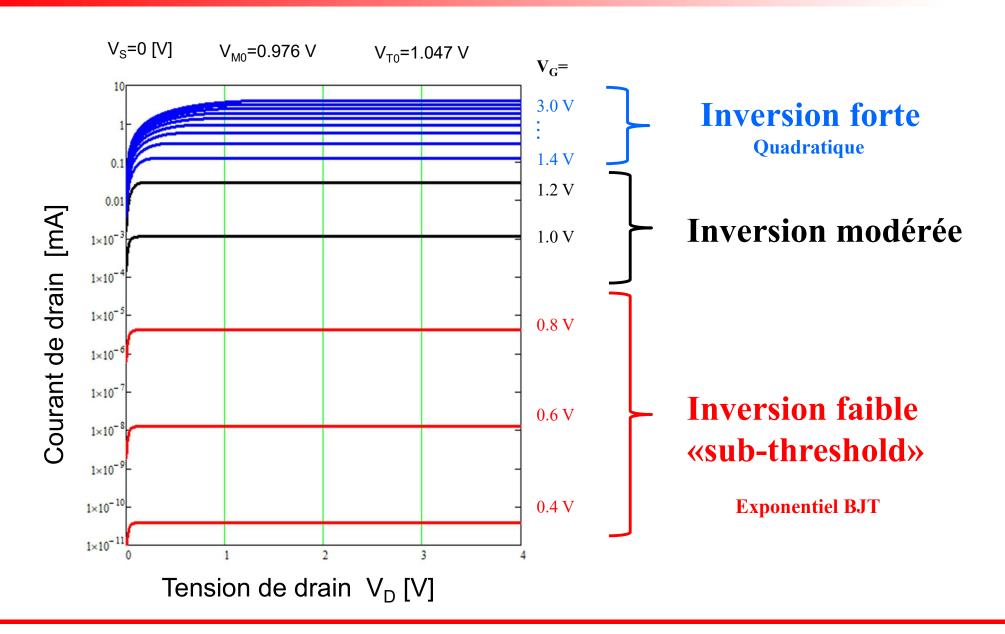

# 10.3: Fonctionnement « sub-threshold »

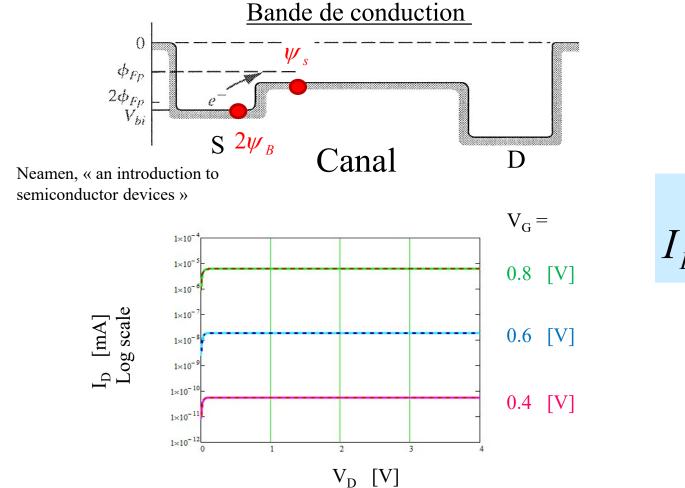

# Fonctionnement « sub-threshold »: inversion faible

- Comportement similaire à un transistor bipolaire npn

- Pas de champ électrique → courant de diffusion

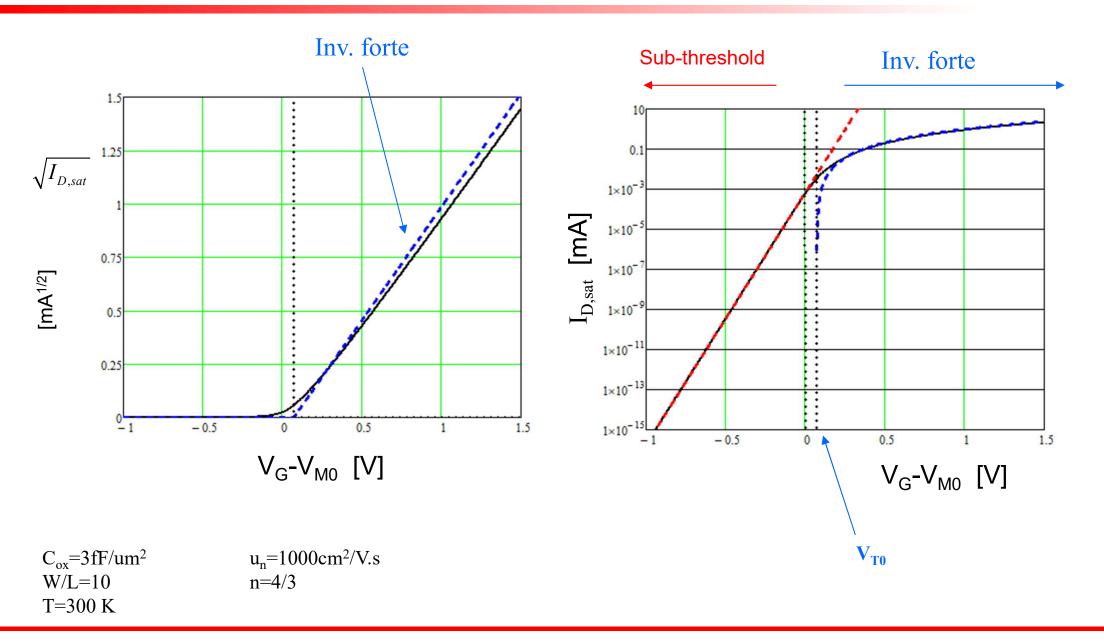

# Opération « sub-threshold »: exemple en mode actif $(V_D > V_{D,sat})$

$u_n = 1000 \text{ cm}^2/\text{V.s}$ n = 4/3

$S = n \cdot U_T \cdot Ln(10)$

$300K \rightarrow S=n.60 \text{ mV/dec.}$

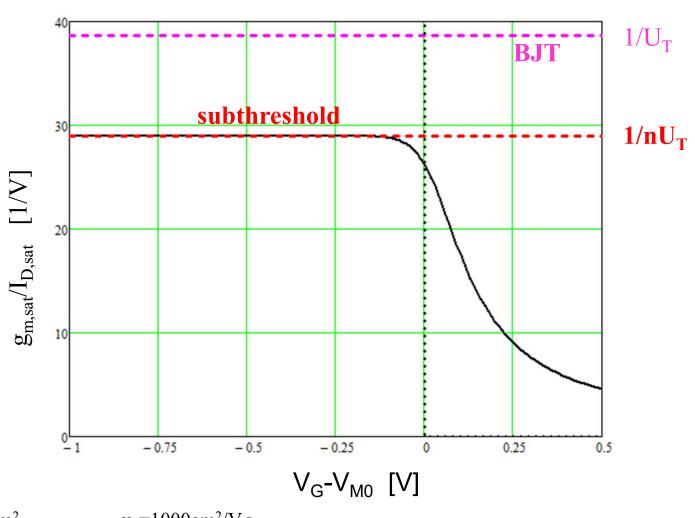

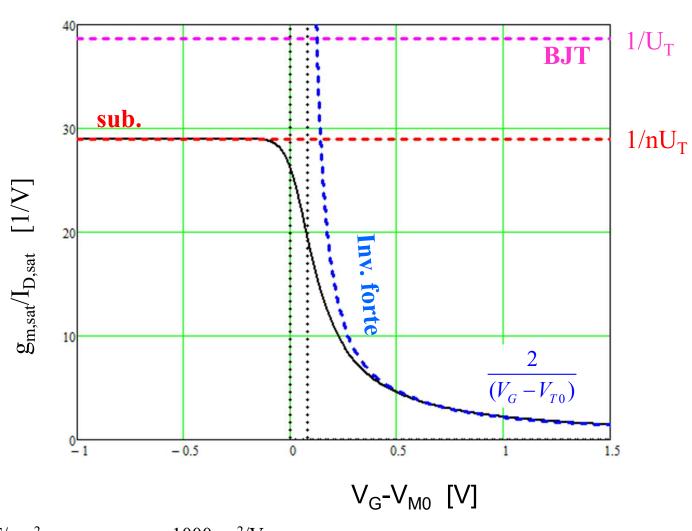

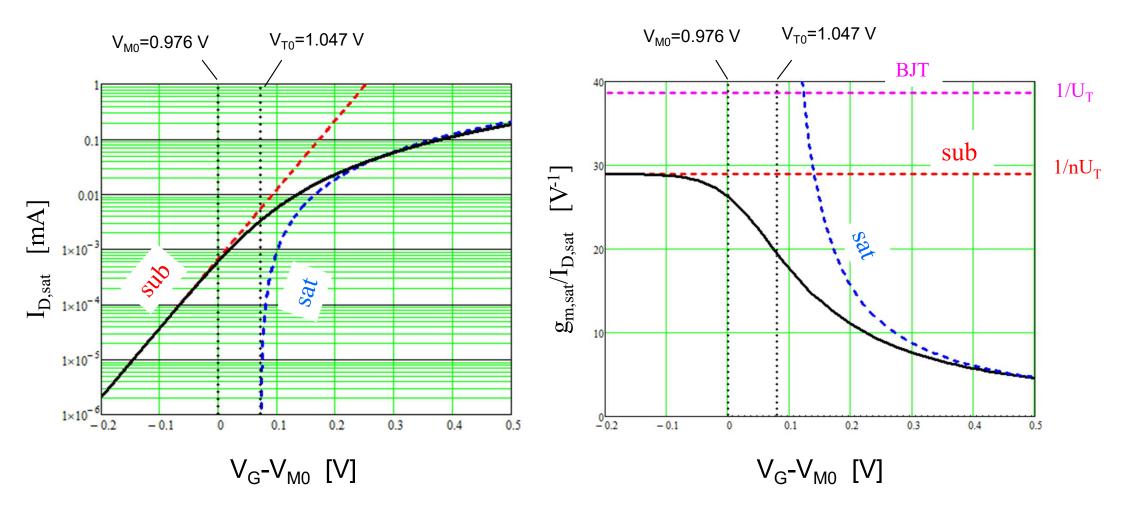

# Transconductance en saturation: g<sub>m</sub>/I<sub>D</sub>

Transconductance définition

$$g_{m,sat} \equiv \frac{\partial I_{D,sat}}{\partial V_G}$$

$$u_n = 1000 \text{cm}^2/\text{V.s}$$

$n = 4/3$

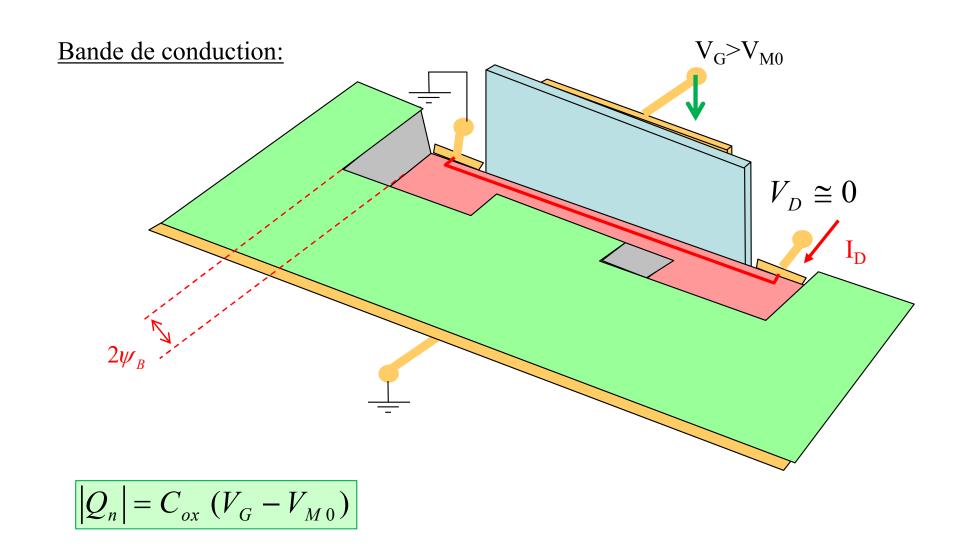

# 10.4: NMOS en inversion forte, régime linéaire

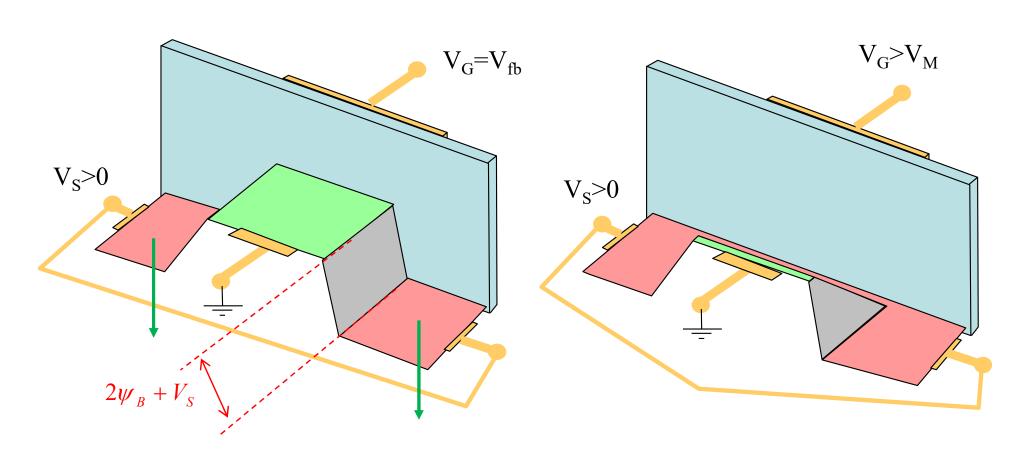

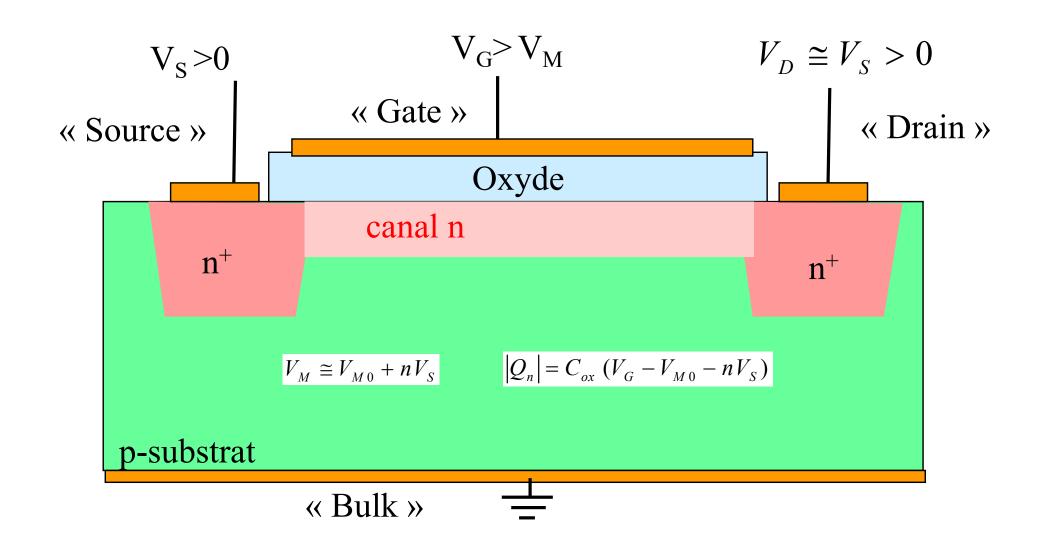

# Influence de V<sub>S</sub>

**Threshold:**

Inversion:  $V_G > V_M$

$$V_G - V_{M0} \cong n \cdot (\psi_s - 2\psi_B) \implies V_M - V_{M0} \cong n \cdot V_S$$

$$Q_n = -C_{ox}(V_G - V_{M0} - nV_S)$$

# Influence de V<sub>S</sub>

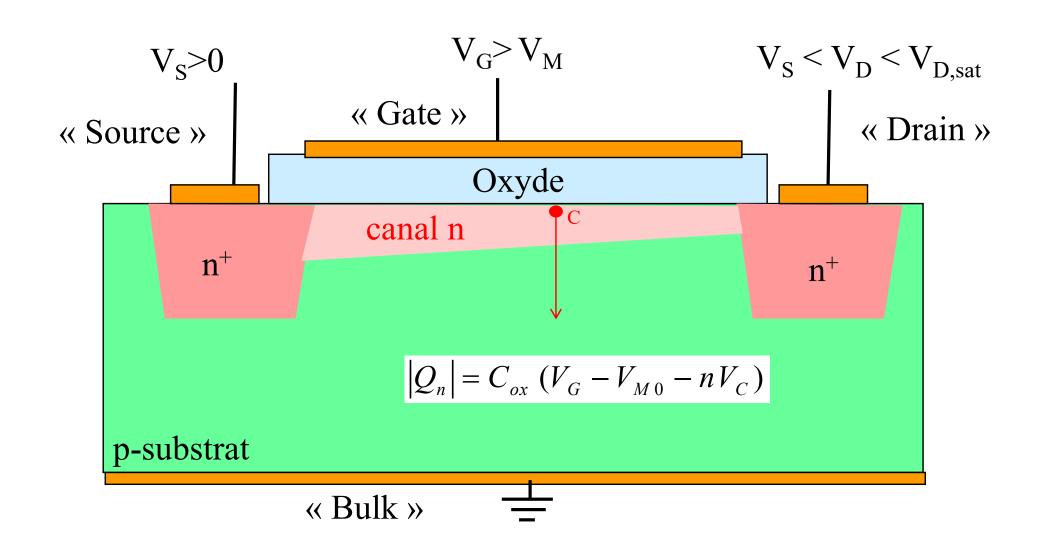

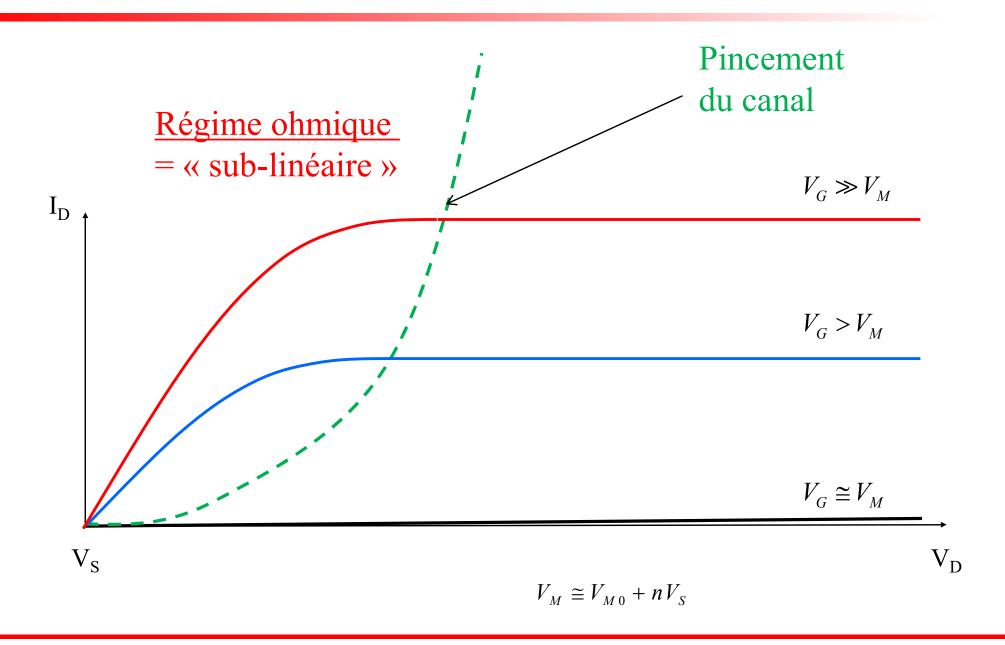

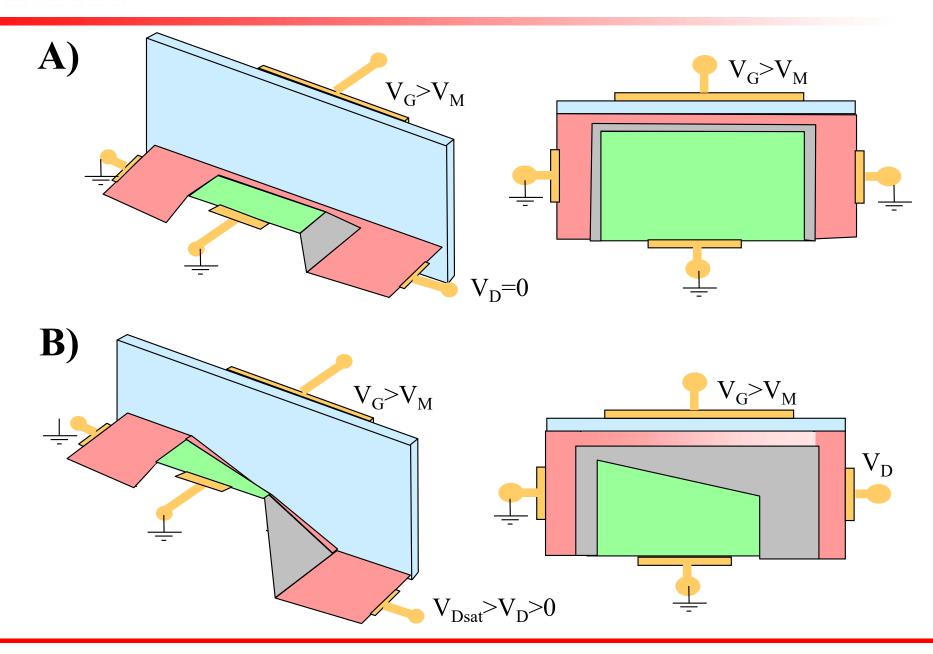

# NMOS en inversion forte, régime ohmique

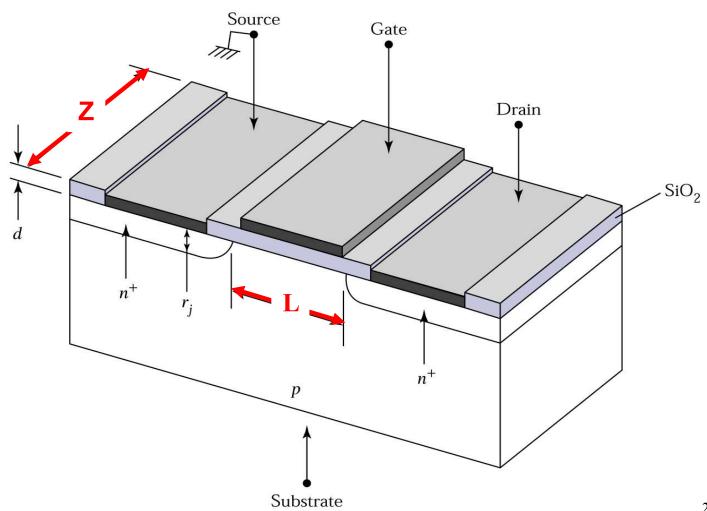

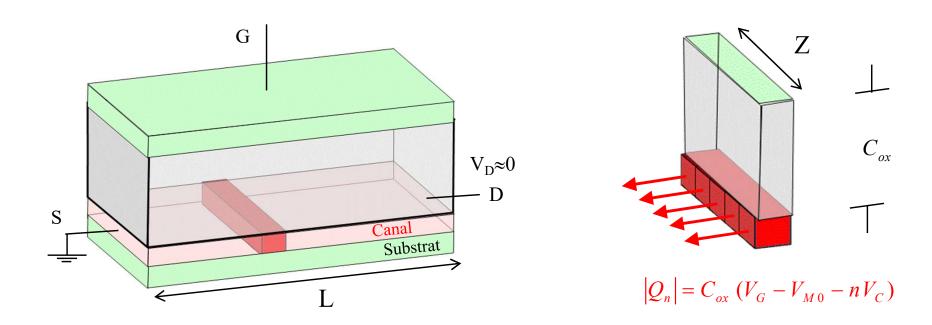

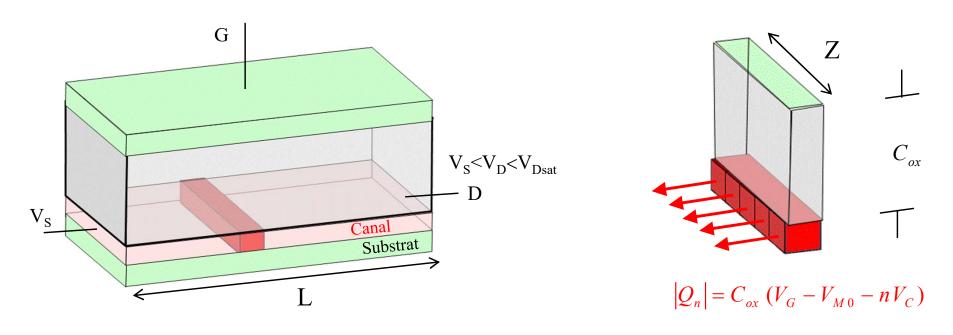

# Régime FET ohmique: vision 3D

Les charges dans le canal diminuent lorsqu'on s'approche du drain

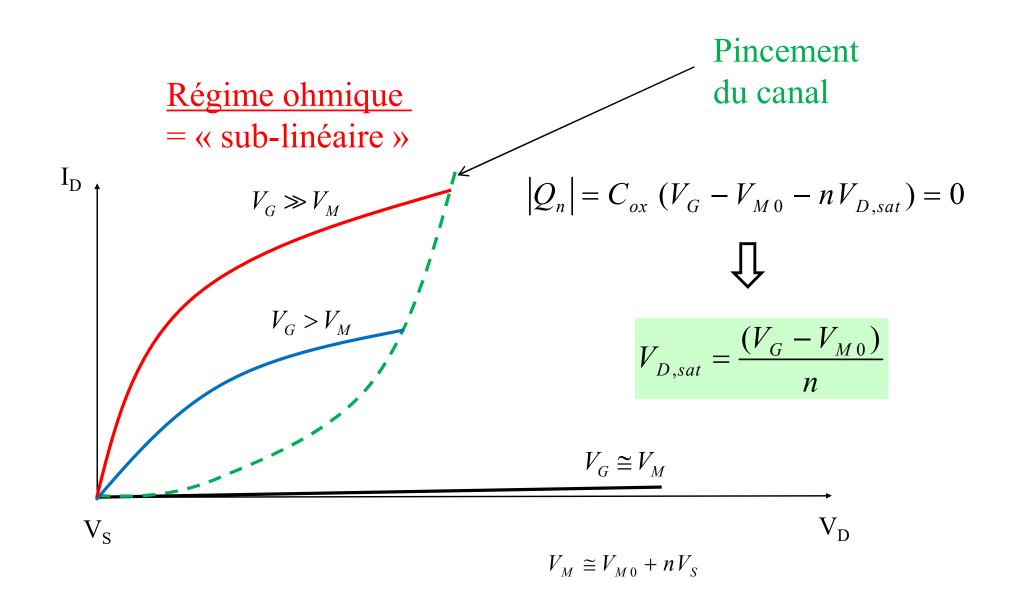

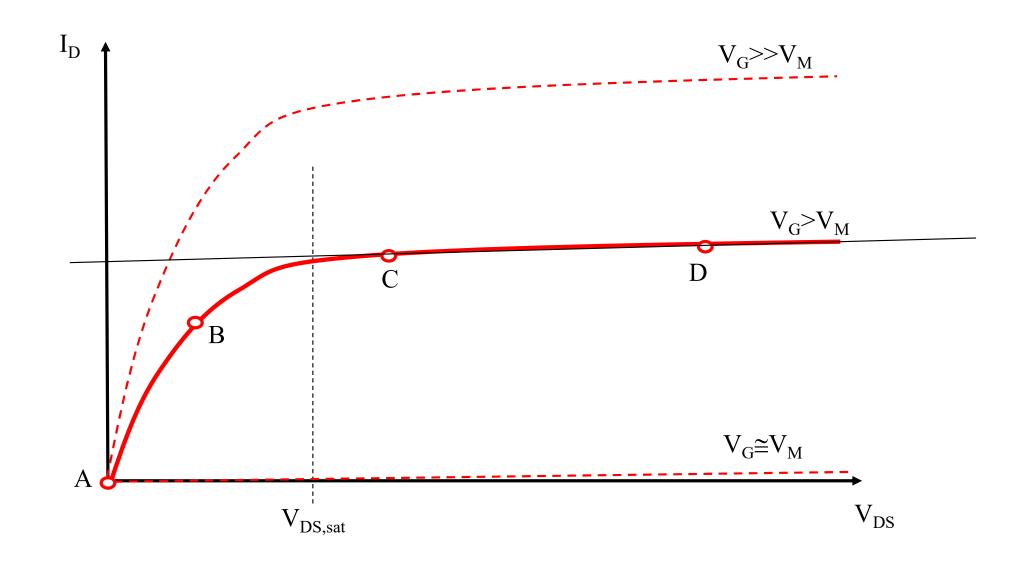

# Régime FET ohmique: courbes caractéristiques

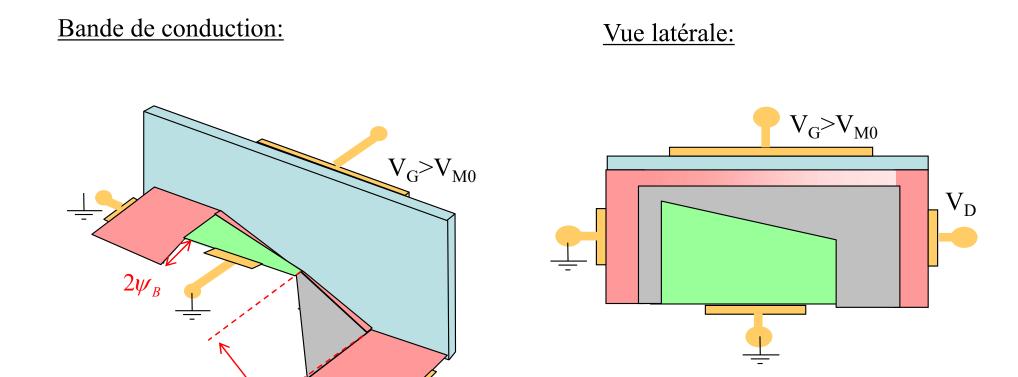

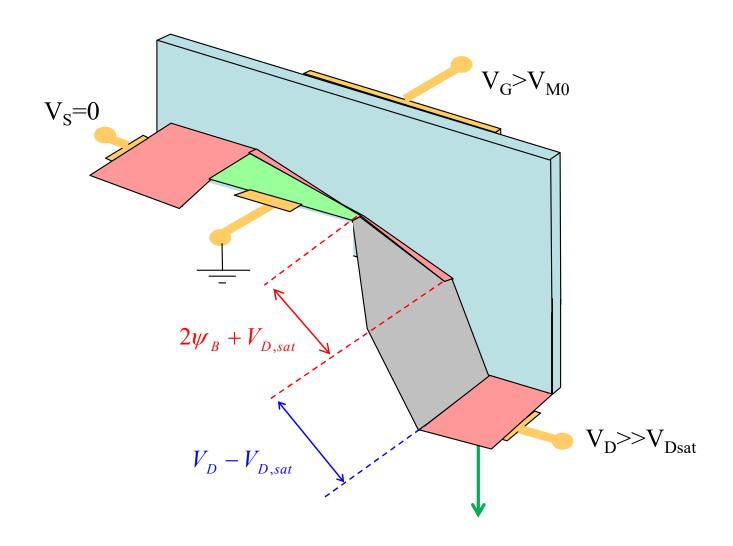

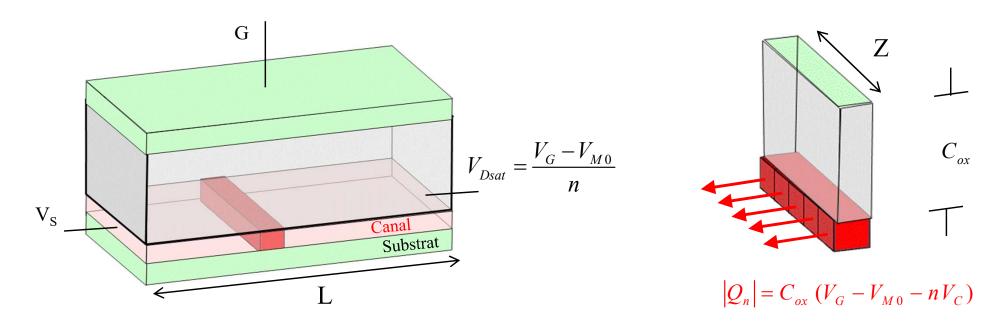

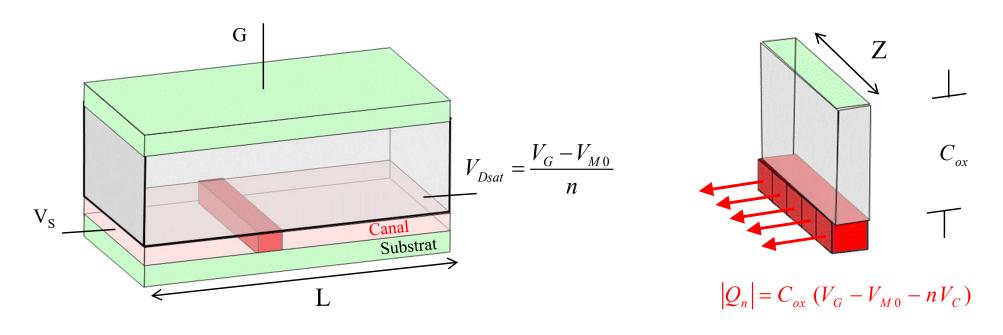

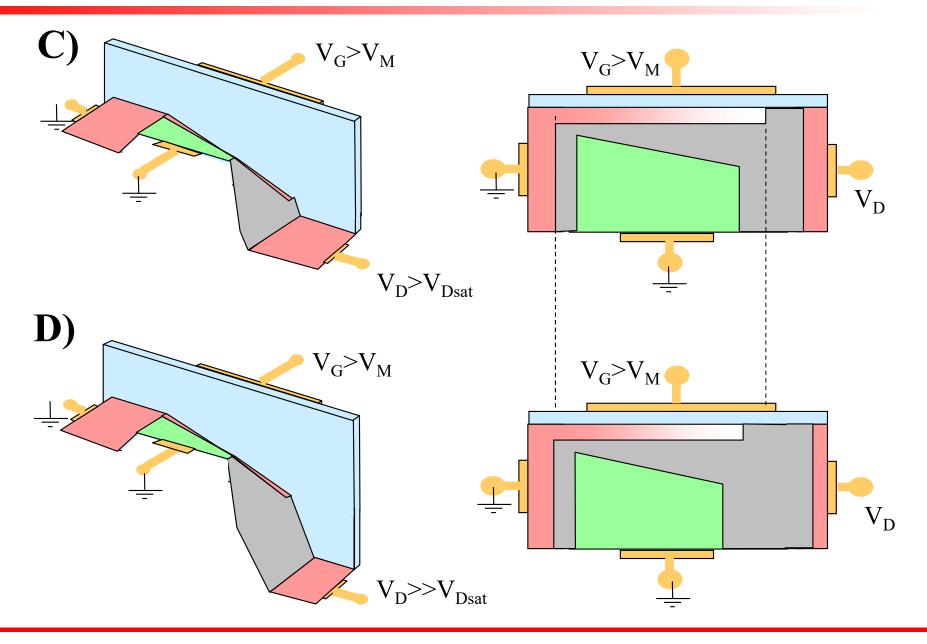

## Pincement du canal: vision 3D

# Bande de conduction: $V_{G} > V_{M0}$ $V_{G} > V_{M0}$ $V_{W} > V_{M0}$ $V_{W} > V_{W} > V_{W}$

$V_D > V_{Dsat}$

$V_D - V_{D,sat}$

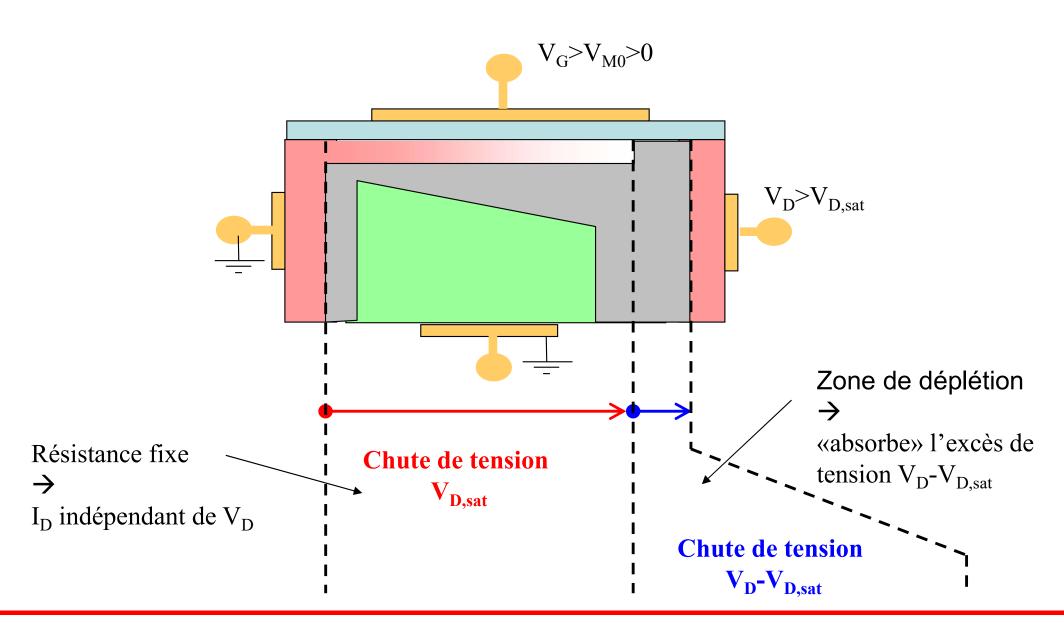

# Régime de saturation

## Pincement du canal NMOS

#### Pincement du canal

# Régime FET idéal

$$\frac{I_D}{Z} = Q_n \cdot v = \dots$$

Développez l'expression du courant en considérant la charge et la vitesse moyenne au milieu du canal

#### A) Régime ohmique

$$\frac{I_D}{Z} = \left(\frac{Q_{n,S} + Q_{n,D}}{2}\right) \cdot \left(\mu_n \left| \vec{E} \right|\right) = C_{ox} \left(V_G - V_{M0} - n \frac{V_D + V_S}{2}\right) \cdot \left(\mu_n \frac{V_D - V_S}{L}\right)$$

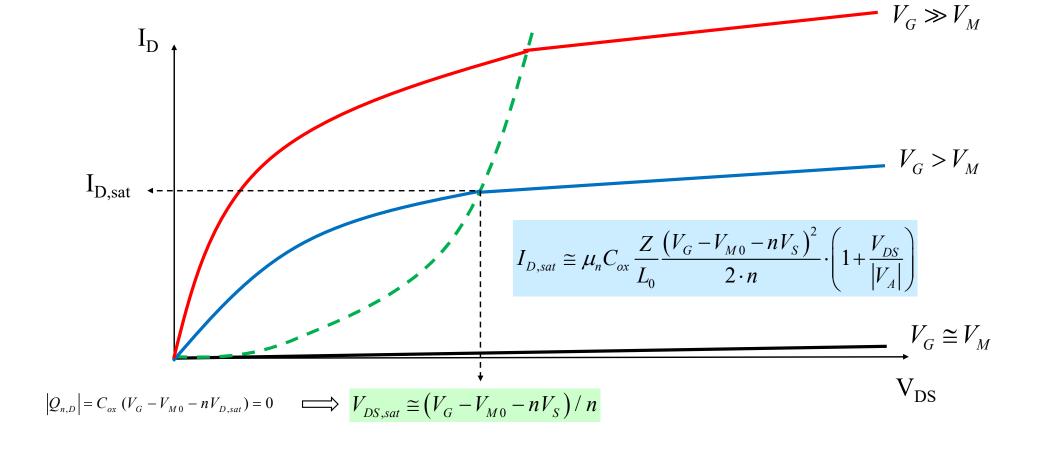

#### B) Régime de saturation

$$\frac{I_D}{Z} = \left(\frac{Q_{n,S} + Q_{n,D}}{2}\right) \cdot \left(\mu_n \left| \vec{E} \right|\right) = \frac{C_{ox} \left(V_G - V_{M0} - nV_S\right)}{2} \cdot \left(\mu_n \frac{V_{D,sat} - V_S}{L}\right)$$

#### B) Régime de saturation

$$\frac{I_D}{Z} = \left(\frac{Q_{n,S} + Q_{n,D}}{2}\right) \cdot \left(\mu_n \left| \vec{E} \right|\right) = \mu_n C_{ox} \frac{\left(V_G - V_{M0} - nV_S\right)^2}{2 \cdot n \cdot L}$$

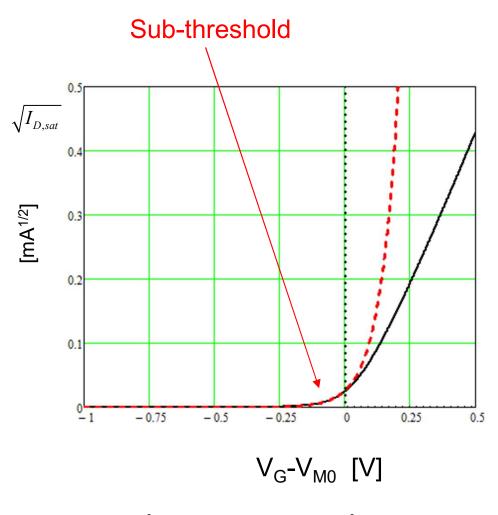

### Inversion forte en saturation

$$(V_D > V_{D,sat})$$

### Transconductance en saturation:

$g_{m}\!/I_{D}$

Transconductance définition

$$g_{m,sat} \equiv \frac{\partial I_{D,sat}}{\partial V_G}$$

$$u_n = 1000 \text{cm}^2/\text{V.s}$$

$n = 4/3$

# Résumé NMOS : comportement en régime FET en fonction de la tension de drain

## Résumé NMOS (1)

### Résumé NMOS (2)

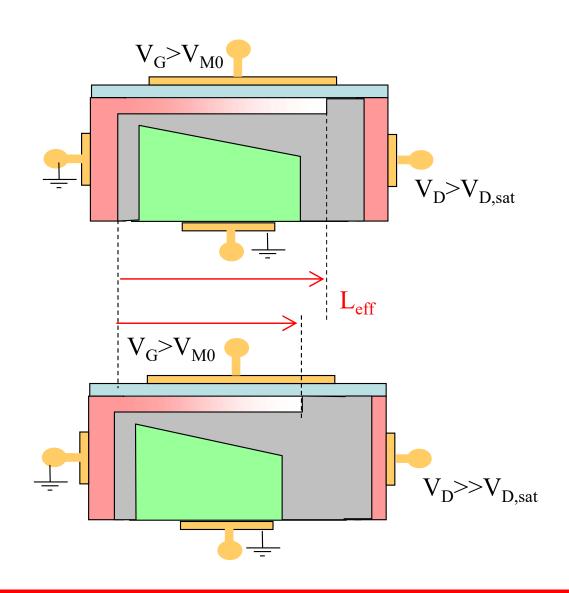

### Modulation de la longueur du canal

Le canal se rétrécit lentement avec l'augmentation de la tension de drain  $V_D$ .

→ Le courant de drain augmente légèrement

$$I_{D,sat} \approx \frac{1}{L_{eff}} = \frac{1}{L_0} \cdot \left( 1 + \frac{V_{DS}}{|V_A|} \right)$$

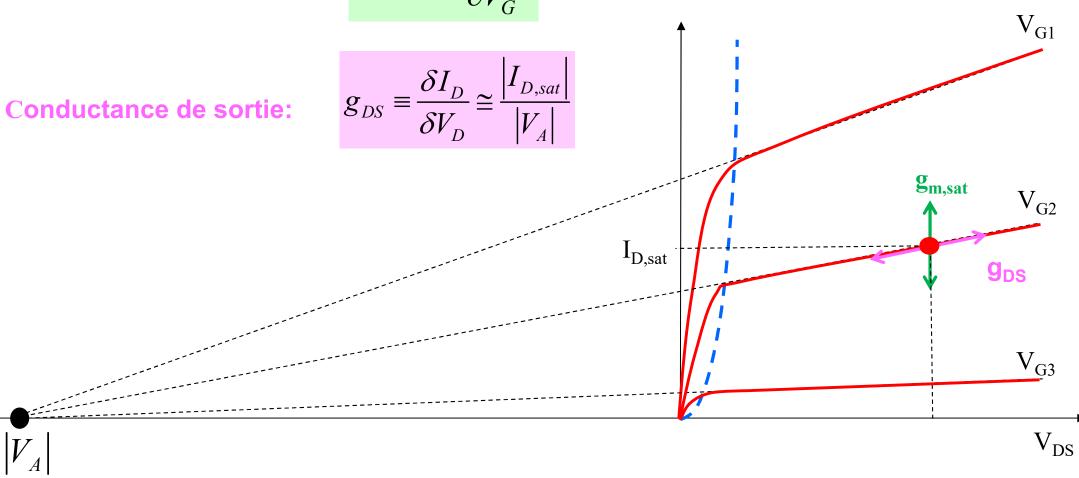

# Courbes de sortie en mode FET avec modulation de la longueur du canal

$$\frac{g_{m,sat}}{I_{D,sat}} \equiv \frac{1}{I_{D,sat}} \frac{\partial I_{D,sat}}{\partial V_G} \cong \frac{2}{(V_G - V_{M0} - nV_S)}$$

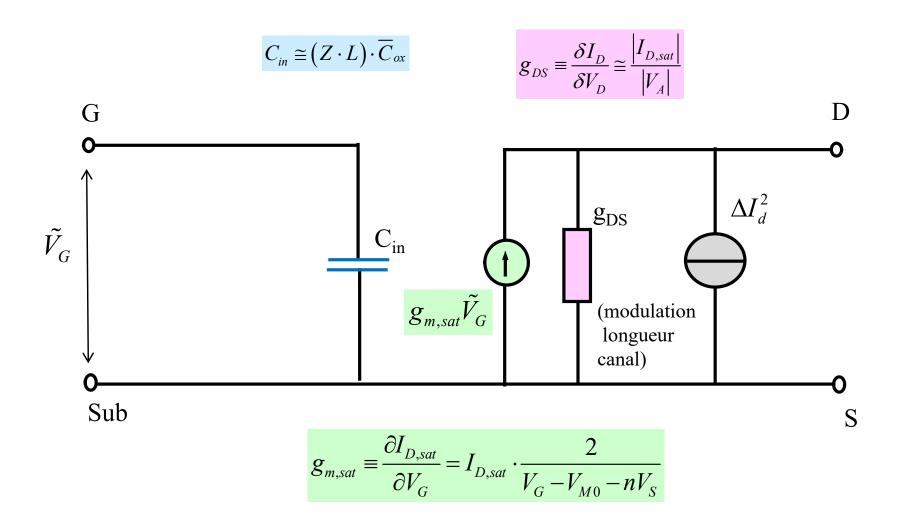

### 10.5: circuit petit signaux : Conductances en mode actif

**Transconductance:**

$$g_{m,sat} \equiv \frac{\partial I_{D,sat}}{\partial V_G}$$

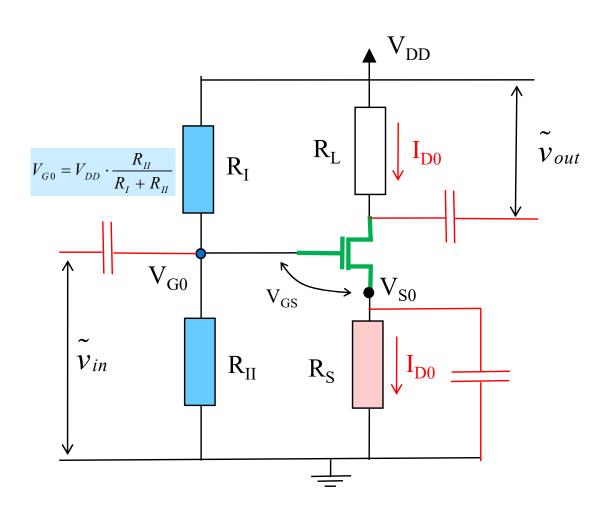

### Circuit petits signaux simplifié

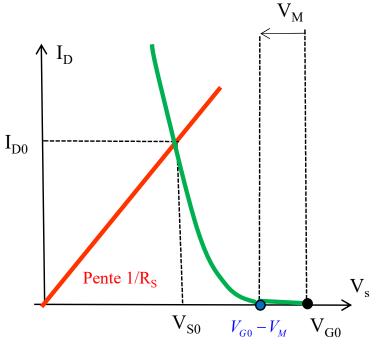

### Polarisation du NMOS: point de travail

Entrée sur la capacité de gate  $\rightarrow$  R<sub>in</sub> infinie pour  $\omega$ =0.

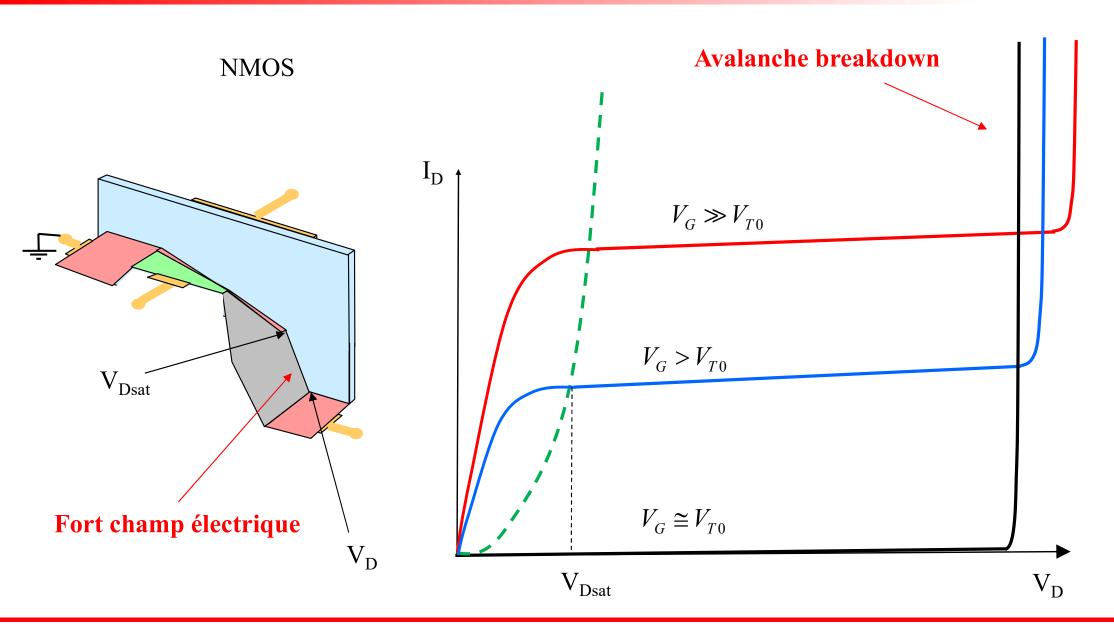

### Avalanche breakdown

### Courant de drain: Modèle EKV

## Comparaison des modèles

$$u_n = 1000 \text{cm}^2/\text{V.s}$$

$n = 4/3$

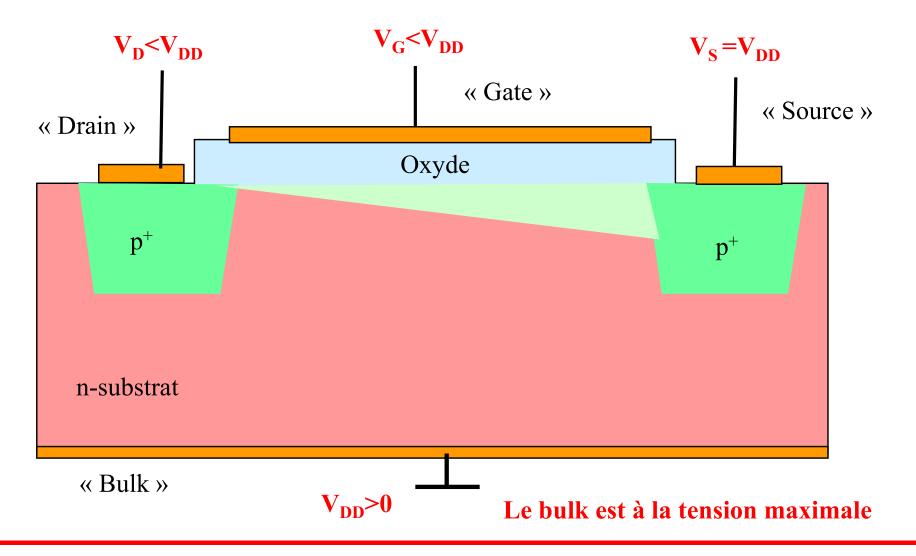

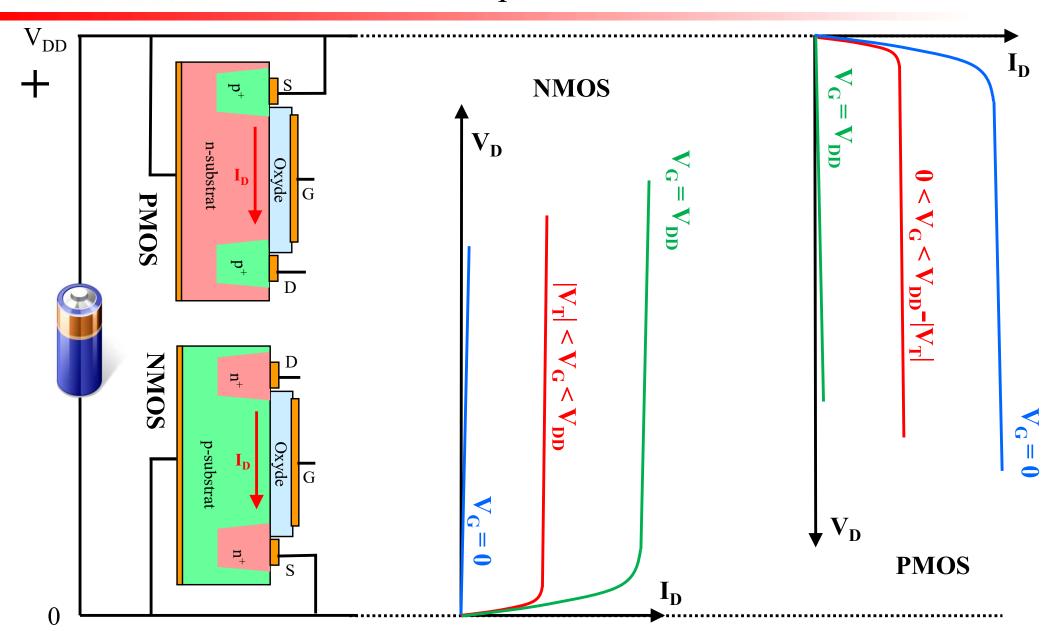

### PMOS: MOSFET à canal P

Le drain et le gate sont à des tensions inférieures au bulk

La source est à la tension de bulk

# Comparaison NMOS et PMOS: «Complémentarité»

# Exercice E10.2: VLSI et dissipation d'énergie

Considérons un chip avec une "Very Large Scale Integration" (VLSI) travaillant à température ambiante. Il contient  $10^9$  NMOS, tous "fermés" donc avec une tension de gate  $V_G=0$ . Le courant "subthreshold" est exprimé par:

$$I_{D,sub} \cong I_{0,sub} \cdot e^{q(V_G - V_T)/nkT}$$

avec  $n = 1.33$

- A) Le courant à  $V_G=0$  V pour une tension de threshold  $V_T=0.5$  V est de 4 pA par transistor. Quelle est la consommation en courant de tout le chip lorsque les transistors sont tous fermés ?

- B) Nous diminuons la tension de threshold à  $V_T$ =0.25V. Quelle est maintenant la consommation en courant de tout le chip lorsque les transistors sont tous fermés ?

Commentaire: Cet exercice vise à montrer que le courant "subthreshold" pose une limite inférieure pour la tension de voltage, ceci afin d'assurer une bonne "fermeture" des transistors. Dans un micro-processeur, il y a en effet beaucoup plus de transistors au repos que de transistors "ouverts".

# Exercice E10.3: question de réflexion

### Répondez à la question de réflexion

Quelles sont les contraintes sur l'oxyde d'une structure MOS ?

Discutez le cas d'une structure MOS sur substrat p en inversion forte (transistor) et celui de la même structure en déplétion profonde (CCD).

Exemple:

on applique 5V sur le gate. Dans lequel des deux cas (inversion forte ou déplétion profonde) le champ électrique dans l'oxyde est-il le plus important ? (risque de claquage!).

### Exercices E10.4

#### E10.4: MOSFET avec grille et drain court-circuités

- a) Lorsque la tension de drain et celle de gate sont court-circuitées ( $V_G=V_D$ ), comparez la tension de drain  $V_D$  avec la tension de saturation  $V_{D,sat}$ . (nous supposons une tension de threshold  $V_{M0}$  positive pour le NMOS, et la source et substrat connectés à la masse)

- b) Que peut-on en déduire sur le régime de fonctionnement du NMOS ?

- c) Déterminez la relation courant-tension de ce transistor NMOS avec la grille et le drain court-circuités.

- d) Comment peut-on à partir de la mesure de cette caractéristique déterminer la tension de seuil ?